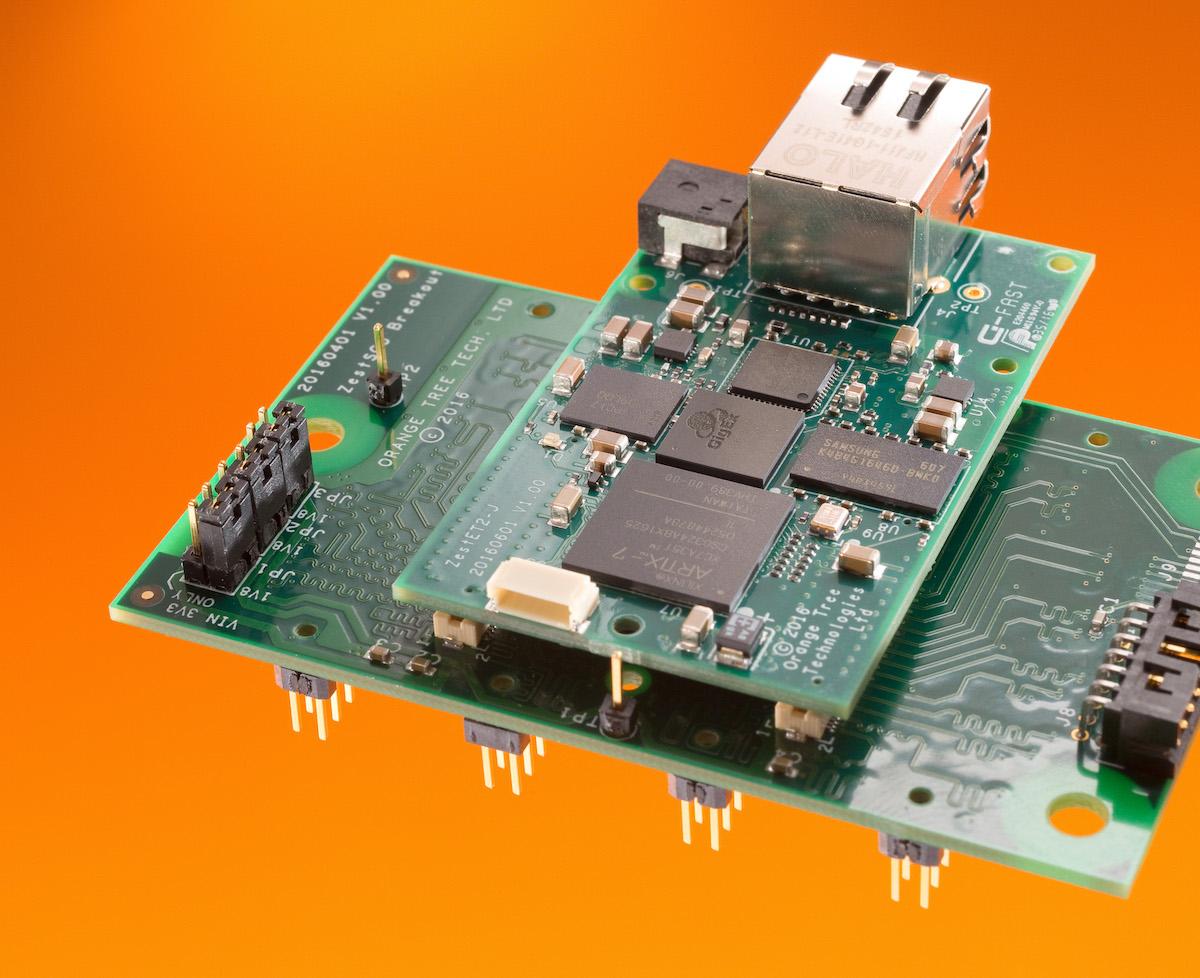

ZestET2-NJ 以太网 FPGA板采用Xilinx Artix-7,高性能TCP/IP减负引擎

ZestET2-NJEthernetFPGAModuleTheZestET2-NJ是一款简单易用的FPGA板,它采用XilinxArtix-7可编程FPGA已一个性能非常高的TCP/IP减负引擎(TOE)芯片.,用于数据流高速处理以及数据采集和控制。ComparedwithZestET2-J,ZestET2-NJdoesnotincludetheEthernetjackorpowerjacktominimisetheoverallheightofthefinalsolutionincludingcarrierboardandtoallowflexiblepositioningoftheconnectorsintheuser'senclosure.Itprovidesasimplebridgebetweenahighspeedcomputernetworkandaprogrammabledigitalinterface.TheTOEsustainsadatarateover100MBytes/sineachdirectionandincludesauserprogrammableCPUforoptionalhigherlevelprotocols.OrangeTree'sproprietaryGigExpeditechip"GigEx"isaTOEthathandlesalltheEthernetcommunicati***protocols.Thisle***estheArtix-7FPGAcompletelyfreefortheuser'sapplication,andmeanstheuserdoesnotrequireanyknowledgeofEthernetprotocols.WiththemainprocessingengineimplementedinTOEha***are,sustaineddataratesover100MBytes/secareachieved.ThethirdgenerationofOrangeTree’scustomGigExchipprovidesauser-programmableCPU.Thisiscompletelyfreefortheusertoprogram,forexamplewithhigher-levelEthernetprotocolssuchasGigEVisionandIndustrialEthernet,oritcanbeleftunprogrammed.YoucanreadmoreaboutGigExhere.Withitscompactformfactor(40mmx50mm),themoduleisideallysuitedtointegrationinembeddedsystemsandOEMequipment.ItfeaturesauserprogrammableXilinxArtix-7FPGA,coupledwith512MBytesofhighspeedDDR3memory.TheFPGAcanbeprogrammedfromon-boardFlash,EthernetorJTAG.Forevaluationthereisabreakoutboard***ailable.ZestET2-NJ-BRKconnectstheUserFPGAIOpinstoanFMCconnectoranda0.1”pitchheader.ItincludesallpowersuppliesfortheZestET2-NJandtheFMCandispoweredfrom12V.ItalsohasthestandardXilinxJTAGheaderfortheZestET2-NJUserFPGAandtheFMC.BenefitsEasytousewithnodetailednetworkingknowledgerequiredOfferssimpleaccesstoveryfastdataratesoverGigabitEthernetwithouth***ingtointegratecomplexnetworkingha***areandsoftwareDevicesconnectedtoUserFPGAcancommunicateviaEthernetwithoutusingaprocessororincurringprocessoroverheadsVirtuallynoFPGAresourcesusedfornetworkcommunicati***,somostofFPGA***ailablefordataprocessingCanbeextendedtoapplicationlayerprotocolsrunningaboveTCPorUDPeitherinUserCPUorUserFPGAFeaturesMorethan100MBytes/secsustaineddatarateineachdirectionoverGigabitEthernetXilinxArtix-7UserFPGAand512MBytesDDR3memory105UserIOpinsGigExha***areTOEforUDPandTCP/IPoffloadUserCPUwithintheGigExTOEforuserdefinedapplicationlayerprotocols(orcanbeleftunprogrammed)Real-timeEthernetextensi***PrecisionTimeProtocol(PTP)andSynchronousEthernet(SyncE)SinglepowersupplyandlowexternalcomponentcountFreeWindowstoolsbasedonGCCandEclipsefortheGigExUserCPUFreetools***ailablefromXilinxforcreatingFPGAdesigns(Webpack)WindowsandLinuxsoftwaresupportforconfiguringandcommunicatingwiththeUserFPGALogiccoresforallFPGAinterfacesReferencedesigns(includingC,VHDLandVerilogsource)ZestDAQframeworkoflogiccoresandhostsoftwareforquickimplementationofdataacquisitionandcontrolapplicati***)